线程级并行

引言

- 多处理器: 由紧耦合处理器组成的计算机, 这些处理器的协调与使用通常由单个操作系统控制, 它们通过共享地址空间来共享存储器

- 通过两种不同的软件模型来利用 TLP

- 并行处理: 运行一组紧密耦合的线程, 协同完成一项任务

- 多道程序: 由一位或多位用户发起的多个相对独立的进程 (这是请求级并行的一种形式, 每一个请求之间相互独立)

- 可以由在多处理器环境下执行的应用程序完成, 也可以由多个独立运行的应用程序完成 (多道程序)

- 通过两种不同的软件模型来利用 TLP

多处理器体系结构: 问题与方法

- 粒度大小: 分配给一个线程的计算量

- 线程级并行与指令级并行的重要区别: 线程级并行是由软件系统或程序员在较高层级确定的, 这些线程由数百条乃至数百万条可以并行执行的指令组成

- 线程还能够发挥出数据级并行的优势, 但是数据的粒度必须足够大才能够高效的利用并行

- 例如, 尽管向量处理器或 GPU 能够高效地实现短向量运算的并行化, 但当并行分散在许多线程中时, 粒度大小可能会非常小, 以至于开销使得在 MIMD 中利用并行性的成本非常高

- 共享存储器的多处理器分类:

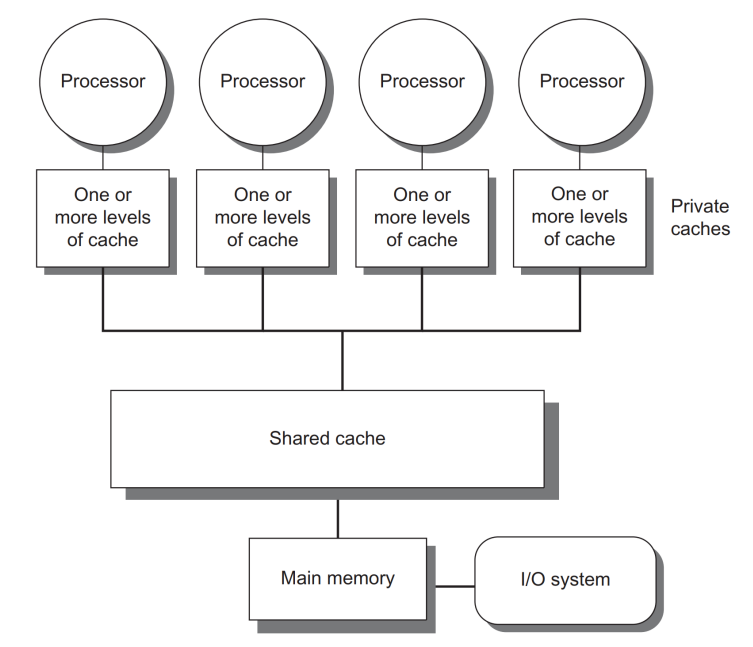

- 对称 (共享存储器)多处理器 (SMP) 或集中式共享存储器多处理器

- 特点:

- 核数量较少

- 因为核少, 所以处理器可以共享一个集中式存储器并且平等地访问它 (对称)

- 在由多个多核芯片组成的多处理器中, 每个多核芯片通常都有独立的存储器

- 有时也称为一致存储器访问 (uniform memory access, UMA): 所有处理器访问存储器的延迟都是一致的, 即使当存储器被分为多个组时也是如此

- 特点:

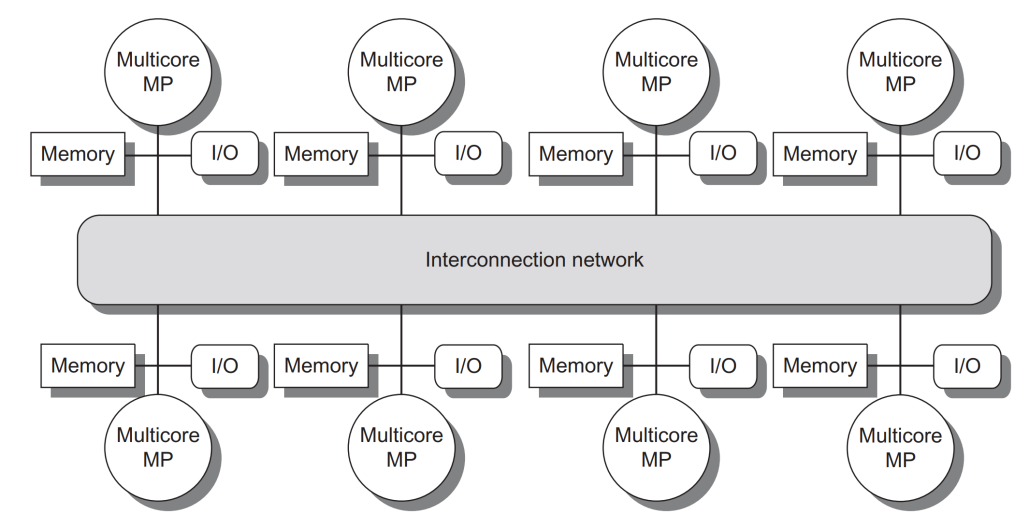

- 分布式共享存储器处理器 (DSM)

- 为了支持更多的处理器, 存储器必须分散在处理器之间, 而不是集中式的

- 既增加了带宽, 也降低了局部存储器的延迟

- 有时也被称为非一致存储访问 (NUMA): 访问时间取决于数据在存储器中的位置

- 缺点: 让处理器之间传送数据的过程变复杂了, 而且需要在软件开发中付出更多努力才能利用分布式存储器提升的存储带宽

- 为了支持更多的处理器, 存储器必须分散在处理器之间, 而不是集中式的

- 对称 (共享存储器)多处理器 (SMP) 或集中式共享存储器多处理器

[!note] 多处理器的分类方式 我们按照存储器的组织方式来称呼多处理器的, 因为处理器的数量可能会随时间变化

并行处理的挑战

- 两个障碍:

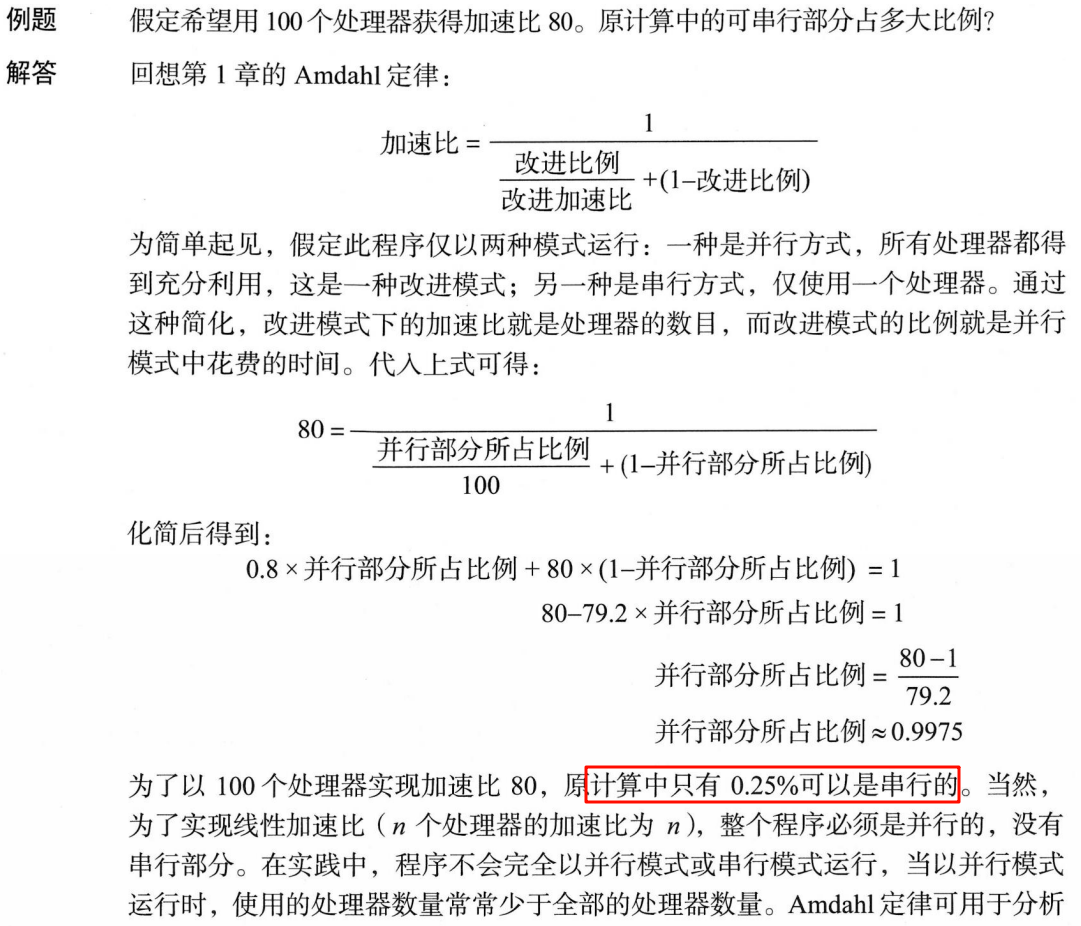

- 程序中有限的并行性: 程序有限的并行性, 使得在任一并行处理器中都难以有良好的加速比

- 在这个例子中, 一个程序只能有 0.25% 是串行的, 而一般的程序难以达到

- 在软件中采用更高并行度的算法

- 在这个例子中, 一个程序只能有 0.25% 是串行的, 而一般的程序难以达到

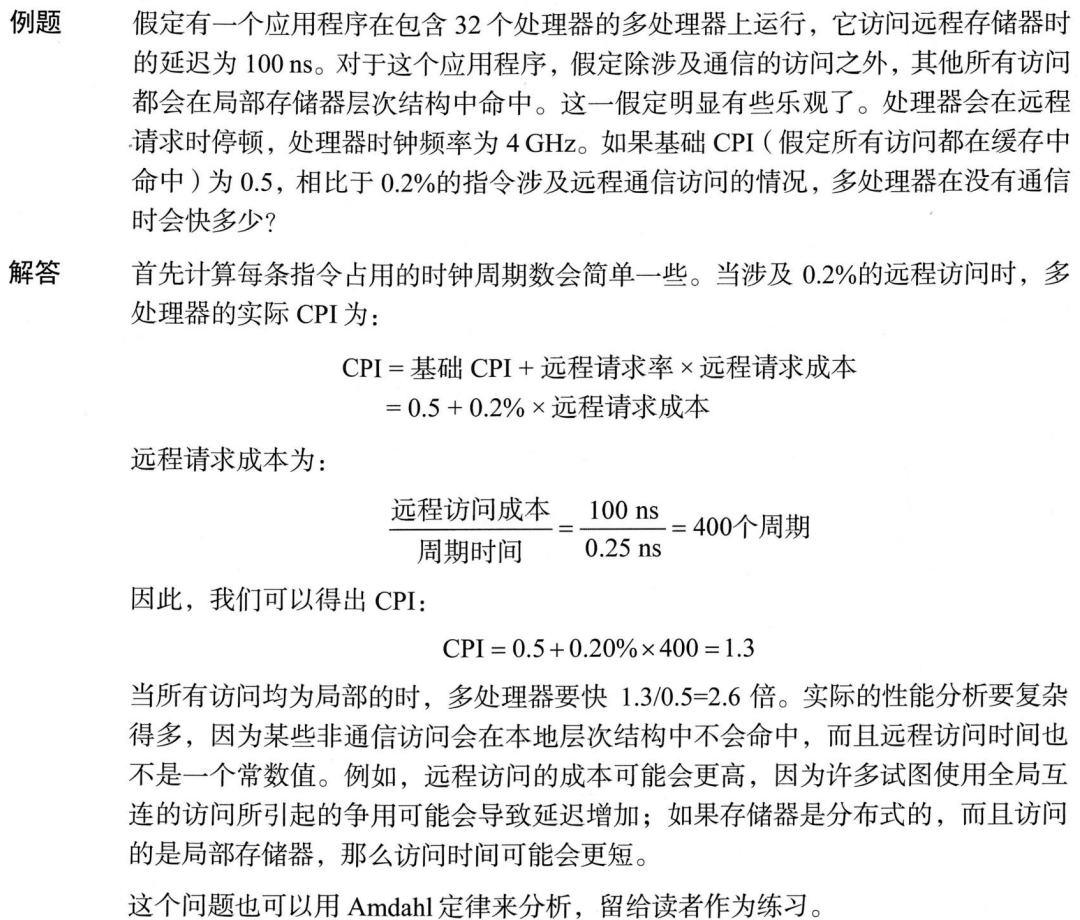

- 较高的通信成本: 不同核之间的数据通信可能耗费 35-50 个时钟周期, 不同芯片上的核之间的数据通信可能耗费 100-500 甚至更多的时钟周期 (本章节重点讨论)

- 通过软硬件降低

- 程序中有限的并行性: 程序有限的并行性, 使得在任一并行处理器中都难以有良好的加速比

集中式共享存储器体系结构

- 采用对称共享存储器的计算机通常支持:

- 对私有数据的缓存: 供单个处理器使用

- 在私有数据项被缓存时, 它的位置被移往缓存, 缩短了平均访问时间并降低了所需要的存储带宽

- 由于没有其他处理器使用数据, 所以程序行为与单处理器中的行为一致

- 对共享数据的缓存: 由多个处理器使用

- 通过读写共享数据来实现处理器之间的通信

- 在缓存共享数据时, 可能会在多个缓存中复制共享值

- 这样可以降低访问延迟和所需要的存储带宽, 还可以减少争用

- 但是引入了新的问题: 缓存一致性

- 对私有数据的缓存: 供单个处理器使用

什么是多处理器缓存一致性

- 缓存一致性问题: 两个不同的处理器是通过各自的缓存来保留存储器视图, 所以对于同一存储地址, 他们可能会看到不同的值

- 缓存一致性问题存在的原因: 既拥有全局状态 (主存) 又拥有局部状态 (缓存)

- 对于编写正确的共享存储器程序至关重要的两个方面:

- 一致性 coherence: 定义了读操作能返回什么值

- 满足以下条件则具有一致性:

- 处理器 P 对位置 X 的读操作跟在 P 对 X 的写操作之后, 并且在 P 的写操作和读操作之间没有其他处理器对 X 执行写操作, 则此读操作总是返回 P 写入的值

- 保持了程序顺序

- 如果一个处理器对位置 X 的读操作紧跟在另一个处理器对 X 的写操作之后, 读写操作的间隔时间足够长, 而且在两次访问之间没有其他处理器对 X 执行写操作, 那么该读操作将返回写入值

- 定义了一致性存储器视图的含义: 如果处理器持续读到一个旧值, 则存储器是不一致的

- 对同一位置执行的写操作时被串行化的, 即在所有处理器看来, 任意两个处理器对相同位置执行的两次写操作顺序相同

- 处理器 P 对位置 X 的读操作跟在 P 对 X 的写操作之后, 并且在 P 的写操作和读操作之间没有其他处理器对 X 执行写操作, 则此读操作总是返回 P 写入的值

- 满足以下条件则具有一致性:

- 连贯性 consistency: 决定一个写入值什么时候被读操作返回

- 一致性 coherence: 定义了读操作能返回什么值

- 两个假定:

- 在所有处理器都看到写入结果之后, 写操作才算完成 (并允许进行下一次写入)

- 对于任何其他存储器访问, 处理器不会改变任何写入顺序